La Ley de Moore, que rigió el progreso electrónico por décadas, alcanzó sus límites físicos. Ahora, un equipo internacional de científicos desafía la lógica horizontal y propone construir chips en vertical, creando un prototipo de 41 capas que promete una revolución para dispositivos flexibles, eficientes y sostenibles, con menor consumo energético.

Durante décadas, la electrónica bailó al ritmo de un mantra inquebrantable: más pequeño es mejor. Una verdad casi bíblica, esculpida en piedra por la famosa ley de Moore, que desde 1965 prometía una duplicación anual de transistores en el mismo espacio. Pero hasta los dogmas más arraigados chocan con la dura realidad de la física. Esa obsesión por lo diminuto, por apretar aún más componentes en un espacio cada vez más exiguo, ha llegado a su límite. Ahora, un equipo internacional de científicos, con una audacia que merece aplauso, nos plantea la solución más elemental y, a la vez, revolucionaria: si no podemos seguir achicando, ¿por qué no empezamos a construir hacia arriba?

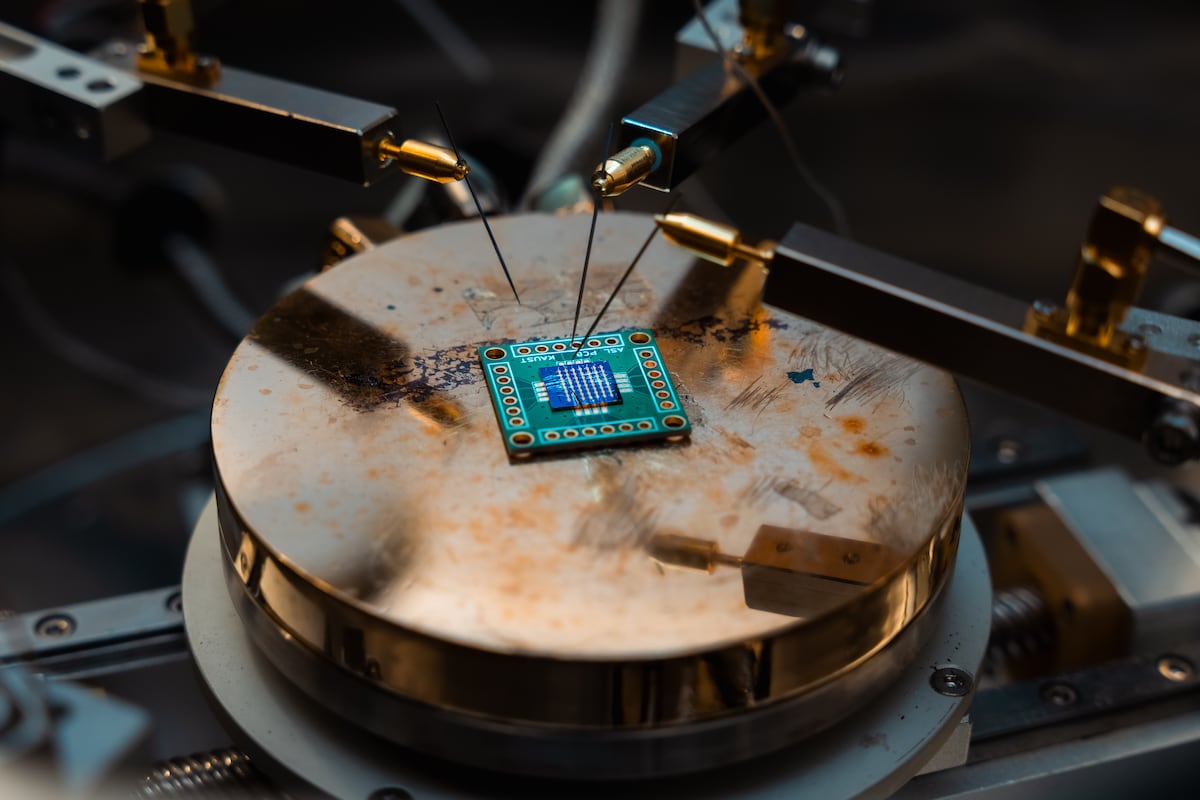

Xiaohang Li, desde la Universidad de Ciencia y Tecnología Rey Abdullah de Arabia Saudí (KAUST), lideró esta cruzada. Su equipo no solo soñó con la verticalidad, sino que la materializó en un chip de 41 capas. Sí, 41 pisos de semiconductores y materiales aislantes, una proeza que empequeñece diez veces cualquier intento anterior. El informe, flamante en la prestigiosa Nature Electronics, es más que un logro técnico; es la llave de entrada a una era de electrónica flexible, eficiente y, por qué no decirlo, mucho más sostenible. Un punto para la innovación con conciencia.

“Tener seis o más capas de transistores apiladas verticalmente nos permite aumentar la densidad de circuitos sin hacer los dispositivos más pequeños lateralmente”, explica Li, desgranando la esencia del avance. Y sentencia, con una claridad que desafía la complejidad técnica: “Con seis capas, podemos integrar un 600% más de funciones lógicas en la misma área que con una sola capa, logrando mayor rendimiento y menor consumo de energía”. Una ecuación que a los gurúes de la eficiencia debe sonarles a música celestial.

Aquella profecía de Moore, ¿cuándo empezó a tambalear? Alrededor de 2010, cuando la escala nanométrica de los transistores se volvió tan ínfima que los mismísimos efectos cuánticos comenzaron a meter la cola, distorsionando su funcionamiento. La física, implacable, le puso un freno. “La ley de Moore está alcanzando sus límites físicos en la microelectrónica de silicio tradicional, pero la innovación continúa en nuevas direcciones. En lugar de seguir reduciendo los transistores, estamos explorando nuevos materiales, nuevas arquitecturas y nuevas posibilidades, como el apilamiento”, afirma Li, reconociendo la encrucijada pero señalando, con optimismo, el camino alternativo.

Rascacielos de silicio: un desafío de altura

Para desentrañar la magnitud del desafío técnico que enfrentó su equipo, Li no duda en recurrir a una metáfora arquitectónica que nos permite visualizar la complejidad: “Piense en cada capa de transistores como el piso de un rascacielos. Si un piso es irregular, todo el edificio se vuelve inestable”. Una imagen poderosa que ilustra la clave de su éxito: dominar la “rugosidad de la interfaz”. Porque en el micro-universo de los chips, cualquier pequeña imperfección entre capas no es un detalle menor; es una sentencia de muerte para el flujo de electrones y, por ende, para el rendimiento general del dispositivo. Ni más ni menos.

El avance no fue solo una cuestión de apilar, sino de reinventar el cómo. Desarrollar estrategias de fabricación completamente nuevas se convirtió en la piedra angular. Y aquí viene el golpe de timón: lograr que todas las capas se depositaran a temperatura ambiente o cercana. ¿Un capricho? No, una jugada maestra para proteger las capas ya construidas. Este proceso a baja temperatura, lejos de ser un mero apócope técnico, es la bisagra que abre las puertas a lo impensable. “La mayoría de los materiales flexibles u orgánicos no pueden soportar altas temperaturas”, explica Li. Y añade, marcando la diferencia: “Los procesos tradicionales de semiconductores a menudo superan los 400 °C, lo que fundiría o deformaría estos materiales”. Al mantener la temperatura controlada, se abre el abanico a sustratos de plástico o polímeros, la materia prima de la electrónica flexible del mañana. ¿Alguien dijo wearables que se adapten a la piel como una segunda piel? Ahí vamos.

Para no dejar lugar a dudas sobre la viabilidad de su audaz diseño, el equipo se lanzó a fabricar 600 copias del chip. Y el resultado fue contundente: todas con un rendimiento similar, confirmando la robustez de la propuesta. Los investigadores utilizaron estos micro-rascacielos para las operaciones básicas, obteniendo un rendimiento comparable a los chips tradicionales, pero con un detalle que no es menor: un consumo energético ridículamente inferior. Hablamos de apenas 0,47 microvatios, una cifra que suena a chiste si se la compara con los 210 típicos de los dispositivos de última generación. ¿El futuro sostenible? Quizás esté en estas pilas de silicio.

Primeras aplicaciones: del cuerpo al hogar, y más allá

Entonces, la pregunta del millón: ¿dónde aterrizará primero esta tecnología? Li, con un optimismo anclado en la realidad, aventura: “Las primeras aplicaciones probablemente serán sensores de salud portátiles, etiquetas inteligentes y pantallas flexibles, donde el bajo consumo y la flexibilidad mecánica son cruciales”. Es decir, dispositivos que convivan con nosotros, casi imperceptibles, sin devorar baterías. Pero la visión va más allá: el equipo ya fantasea con superficies informáticas de gran área, lo que ellos denominan “pieles electrónicas” capaces de sentir, procesar y comunicarse a través de objetos o estructuras enteras. Si bien estos chips apilados no serán el cerebro de las supercomputadoras del mañana, su despliegue masivo en electrodomésticos y dispositivos cotidianos podría tener un impacto monumental: reducir drásticamente la, cada vez más preocupante, huella de carbono de la industria electrónica. Un pequeño paso para el chip, un gran salto para el planeta. ¿O es al revés?

“Los circuitos que desarrollamos están diseñados para estos sistemas, donde la flexibilidad mecánica, el bajo coste y la escalabilidad importan más que la velocidad extrema”, aclara Li, delineando el nicho de mercado y la verdadera fortaleza de su invención. El investigador, con la perspectiva de quien acaba de mover un tablero, sentencia que su trabajo abre una puerta hasta ahora entreabierta en el vasto campo de la informática: “Muestra que el escalado de rendimiento puede continuar, no solo haciendo los dispositivos más pequeños, sino integrándolos de manera más inteligente y eficiente en tres dimensiones.” Una declaración que no solo redefine el «más» en la ecuación de la tecnología, sino que nos invita a mirar hacia arriba, literalmente, para entender el futuro de nuestros gadgets.